- 您现在的位置:买卖IC网 > Sheet目录3862 > PIC16F916-I/ML (Microchip Technology)IC PIC MCU FLASH 8KX14 28QFN

2007 Microchip Technology Inc.

DS41250F-page 17

PIC16F913/914/916/917/946

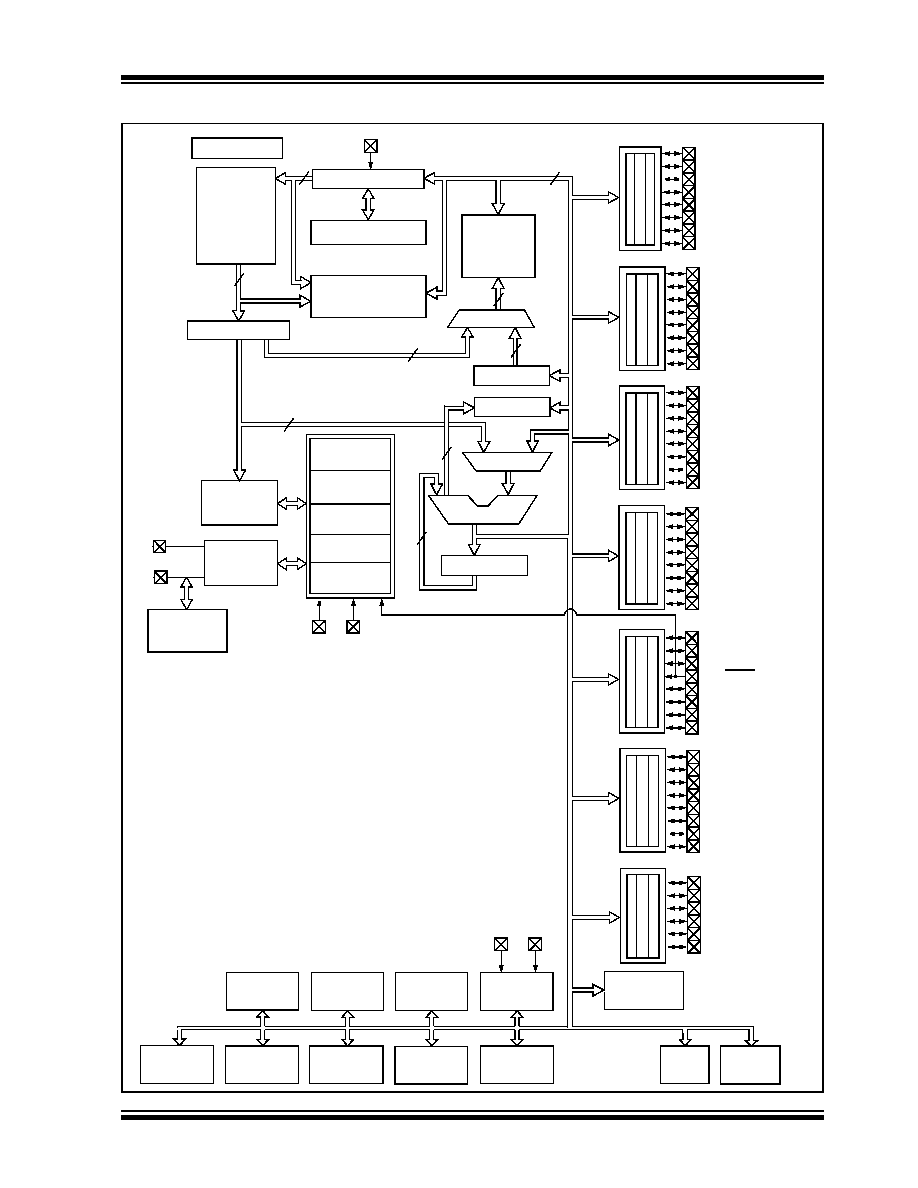

FIGURE 1-3:

PIC16F946 BLOCK DIAGRAM

Power-up

Timer

Oscillator

Start-up Timer

Power-on

Reset

Watchdog

Timer

Brown-out

Reset

RB0

RB1

RB2

RB3

RB4

RB5

RB6

RB7

Flash

Program

Memory

13

Data Bus

8

14

Program

Bus

Instruction Reg

Program Counter

RAM

File

Registers

Direct Addr

7

RAM Addr

9

Addr MUX

Indirect

Addr

FSR Reg

STATUS Reg

MUX

ALU

W Reg

Instruction

Decode and

Control

Timing

Generation

OSC1/CLKIN

OSC2/CLKOUT

PORTA

8

3

8-Level Stack (13-bit)

336 x 8 bytes

8K x 14

VSS

RA0

RA1

RA2

RA3

RA4

RA5

RA6

RA7

Configuration

Internal

Oscillator

VDD

Block

Program Memory Read

PORTC

RC0

RC1

RC2

RC3

RC4

RC5

RC6

RC7

PORTD

(PMR)

PORTB

PLVD

LCD

Data EEPROM

256 bytes

Comparators

SSP

CCP1

CCP2

Timer0

Timer1

Timer2

10-bit A/D

Addressable

USART

PORTE

PORTF

PORTG

RD0

RD1

RD2

RD3

RD4

RD5

RD6

RD7

RE0

RE1

RE2

RE3/MCLR

RE4

RE5

RE6

RE7

RF0

RF1

RF2

RF3

RF4

RF5

RF6

RF7

RG0

RG1

RG2

RG3

RG4

RG5

INT

AVSS

AVDD

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC16C716-20I/P

IC MCU OTP 2KX14 A/D PWM 18DIP

PIC18F26K80-I/SO

MCU PIC 64KB FLASH 28SOIC

PIC18F26J13-I/SS

IC PIC MCU 64KB FLASH 28SSOP

SFW27R-1STE1

SFW27R-1STE1-FFC/FPC CONN

PIC18F66J15-I/PT

IC PIC MCU FLASH 48KX16 64TQFP

PIC24FV32KA302-I/SO

MCU 32KB FLASH 2KB RAM 28-SOIC

PIC24HJ64GP204-I/ML

IC PIC MCU FLASH 64K 44-QFN

SFW27R-2STE1

SFW27R-2STE1-FFC/FPC CONN

相关代理商/技术参数

PIC16F916-I/SO

功能描述:8位微控制器 -MCU 14KB FL 352R 25 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F916-I/SO

制造商:Microchip Technology Inc 功能描述:8 Bit Microcontroller Clock Speed:20MHz

PIC16F916-I/SOG

制造商:Microchip Technology Inc 功能描述:8BIT MCU FLASH SMD 16F916 SOIC28

PIC16F916-I/SP

功能描述:8位微控制器 -MCU 14KB FL 352R 25 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F916-I/SP

制造商:Microchip Technology Inc 功能描述:8 Bit Microcontroller Clock Speed:20MHz

PIC16F916-I/SS

功能描述:8位微控制器 -MCU 14KB FL 352R 25 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16F916-I/SS

制造商:Microchip Technology Inc 功能描述:8-Bit Microcontroller IC

PIC16F916T-E/MLC02

制造商:Microchip Technology Inc 功能描述: